- Leakage power -

- leakage power란 logic의 off mode에서 소비되는 전력입니다.

→ logic이 off mode인데 누설되는 전력이 왜 생기는 것인지 알아보았습니다.

Leakage power가 생기는 이유

- 다이오드 역 바이어스 전류 (Diode reverse bias current)

- 하위 임계 값 누설 전류 (Sub-threshold leakage current)

- Gate 산화물 누출 (Gate oxide leakage)

다이오드 역 바이어스 전류 (Diode reverse bias current)

- 역 바이어스를 걸어줄 경우 barrier가 높아져 전류가 통하지 않아야 하지만 미세하게 통합니다.

* 역 바이어스 : N형 반도체 쪽에는 양극(+), P형 반도체 쪽에는 음극(-)를 연결해 주는 것

역 바이어스를 걸어줄 때 미세하게 전류가 흐르는 이유

- PN 접합 시 전기장(E-field)가 생성됩니다.

- 이 전기장은 bias 여부와 상관없이 정공과 자유전하가 이동 가능 하기 때문에 전류가 발생하게 됩니다.

* P : 정공 (hole) : (+)

* N : 자유전하 (election) : (-)

* PN 접합 : 정공과 자유전하를 접합 시키면 diffusion이 일어나게 된다.

* diffusion : 고밀도에서 저밀도로 정공과 전하가 이동하는 것을 의미

* E-field (Electric field) : 전하를 가진 물체 사이에 작용하는 힘, 전기력을 발생시키는 공간

- PN 접합에서 역 바이어스를 걸어줄 경우 공핍 정공과 전하가 더 모이게 되어 공핍 영역이 넓어집니다.

하위 임계 값 누설 전류 (Sub-threshold leakage current)

- 임계값 보다 낮은 전류이지만 생기는 leakage power

소자의 on/off 조건

- Gate 전압(Vg)이 문턱 전압(Vth) (threshold voltage)보다 높으면 on, 낮으면 off

- Vg < Vth인 경우, 즉 off인 경우에는 전류가 흐르지 않아야 합니다.

Vg < Vth 일 때 전류가 미세하게 흐르는 이유

- 작은 전기장 성분(E-field)으로 인해 미세하게 전류가 발생하기 때문입니다.

Gate 산화물 누출 (Gate oxide leakage)

- Gate oxide란 전압을 이용하기 위해 전자의 이동을 막아주는 절연층을 의미합니다.

(즉 전자의 이동을 차단하는 역할)

- Gate oxide는 실리콘 layer 전체에 높은 전기장을 발생시킵니다.

→ 이 상태에서 gate 단자가 바이어스 되면 정공과 전자들이 실리콘을 통과하면서 전류를 발생시킵니다.

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| LEC란 무엇일까? (what is LEC in vlsi, Formality) (0) | 2022.04.27 |

|---|---|

| Scan(LBIST)란 무엇일까? (what is scan in vlsi, occ, atpg, SA, TD, PLL, At-speed) (0) | 2022.04.15 |

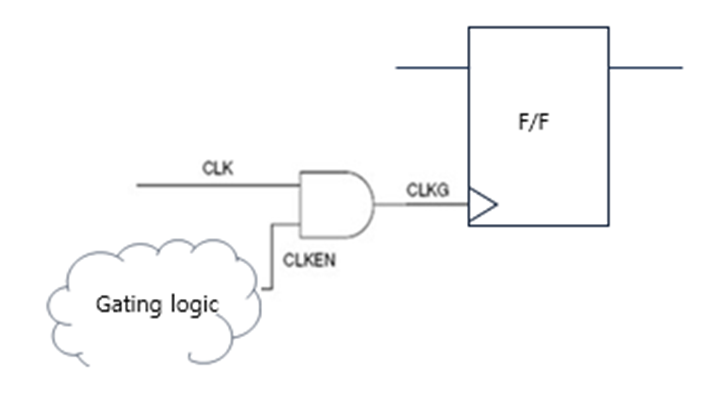

| Low power Techiques란 무엇일까?(what is low power in vlsi, clock gating, isolation, level shift) (0) | 2022.04.12 |

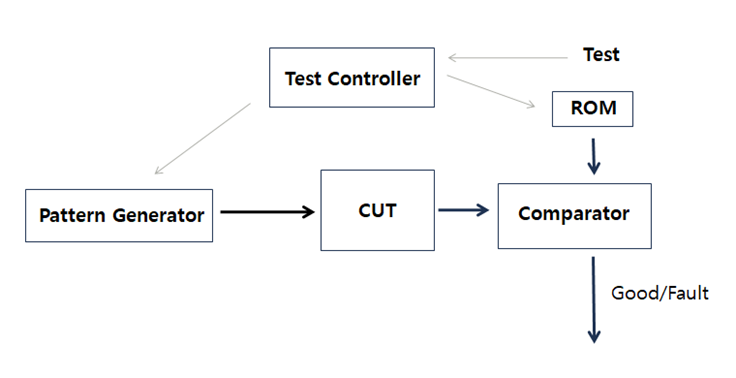

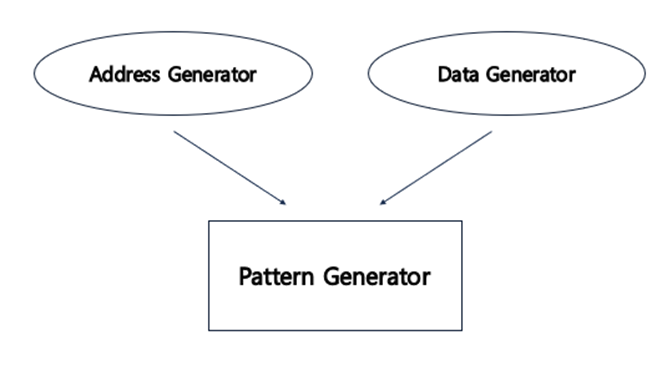

| BIST, BIRA, BISR란? (MBIST,DFT, what is BIST in vlsi?) (0) | 2022.04.05 |

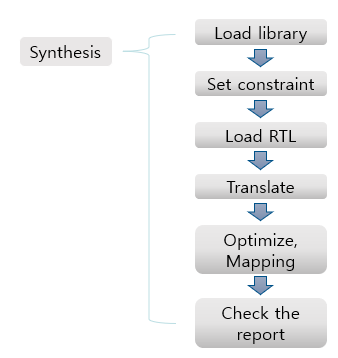

| Back End Flow 란? (what is back end flow in vlsi?) (1) | 2022.04.01 |