- Low power techniques -

- dynamic power와 leakage power를 줄이기 위한 기법으로

비용 절감을 위해 동작 시 필요한 전력을 줄이는 기술입니다.

* dynamic power (동적 전력) : 입력이 활성화 (회로가 동작 될 때) 될 때 사용되는 전력

≒ switching power : capacitor, inductor를 충, 방전 할 때 소모되는 전력

* static power (정전 전력) : 입력이 비활성화 (회로가 동작되지 않을 때) 될 때 사용되는 전력

≒ leakage power (누설 전력) : off mode에서 소비되는 전력

Low power techniques 기법

- Clock gating

- Power gating

- Multi voltage design (Level shifter)

- Isolation cell

- Voltage/Frequency scaling

- Retention register

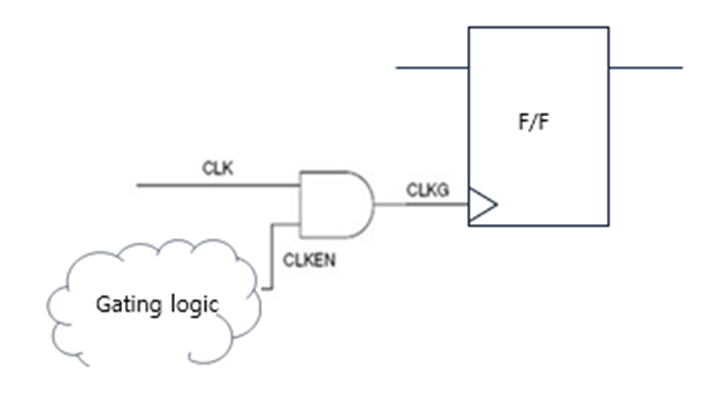

Clock gating

- 사용하지 않는 logic의 clock 공급을 멈추는 방법입니다.

→ Logic의 clock과 clock enable 신호를 AND gate로 연결하면

clock enable 신호에 따라 logic의 clock 공급을 control 할 수 있습니다.

Clock gating이 low power tech인 이유

- 사용하지 않는 logic에 clock을 끊으면 회로의 일부가 비활성화되어 Flip-Flop이 상태를 전환할 필요가 없고

이로 인해 switching power의 소비가 0이 되어 Dynamic power가 감소하기 때문입니다.

Power gating

- 사용하지 않는 logic의 power 공급을 중단하는 방법입니다.

→ Power switch를 사용하여 사용하지 않는 logic을 off 시켜 줍니다.

Power gating이 low power tech인 이유

- Logic이 사용되지 않을 때도 power가 공급되고 있다면 leakage power가 존재합니다.

→ 하지만 power switch를 사용하여 leakage power를 감소시킬 수 있습니다.

Multi voltage design

- Chip 내부에도 domain의 성능에 따라 필요한 voltage가 다릅니다.

→ 가장 높은 voltage를 필요로 하는 domain의 voltage로 맞추는 것이 아닌

각 domain마다 필요한 voltage를 공급받을 수 있게 설계하는 방법입니다.

- Level shift를 사용하여 voltage가 다른 두 domain의 input과 output을 연결시킬 수 있습니다.

* domain : 동일한 전력을 필요로 하는 logic들을 묶어준 것 (VDD, VSS 공유)

Level shift cell

- 서로 다른 voltage를 가진 domain들 사이에 level shift cell을 넣으면 전압을 맞춰줄 수 있습니다.

- 아래 사진과 같이 domain1에서 나온 1.0v의 출력이

level shift를 거치게 되면 0.75v로 바뀌어 domain2로 들어가게 됩니다.

Block(domain)마다 voltage가 다른 이유

- Clock의 입력 속도가 다르기 때문입니다.

Level shift cell이 low power tech인 이유

- 만약 전압을 통일시키면 필요 이상의 전압이 들어가는 domain이 생길 수 있는데,

Level shift cell을 사용하면 각 domain에 맞는 전압을 줄 수 있기 때문입니다.

Isolation cell

- On logic과 (동작 중인 회로) off logic (동작하지 않는 회로)이 있을 때

두 개의 domain 간의 신호를 control 하는 방법입니다.

- Off logic의 출력의 값이 없거나 unknown signal이 나오게 되면 on logic에 영향을 줄 수 있기 떄문에 사용됩니다.

- 두 domain 사이에 isolation cell을 넣어 on logic에 들어가는 신호를 일정하게 유지할 수 있습니다.

Isolation cell의 종류에 따른 출력 값

- AND gate : 0

- OR gate : 1

Isolation cell을 사용하는 이유

- Power switch 사용 시 off logic이 의도하지 않은 신호를 전달하는 것을 방지하기 위해 사용됩니다.

Voltage/Frequency scaling

- Design의 성능에 따라 clock의 주파수를 낮추어 공급 전압을 줄이는 방법입니다.

Retention register

- Block이 on 또는 off 될 때 이전 상태를 유지할 수 있도록 해주는 방법입니다.

→ Power가 off 되기 전에 shadow register에 data를 저장하여 off 상태일 동안 data를 저장해줍니다.

→ Power가 on 될 때 main register로 data가 restore됩니다.

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| Scan(LBIST)란 무엇일까? (what is scan in vlsi, occ, atpg, SA, TD, PLL, At-speed) (0) | 2022.04.15 |

|---|---|

| Leakage power 가 생기는 이유? (logic이 off인데 power가 누설 되는 이유) (0) | 2022.04.13 |

| BIST, BIRA, BISR란? (MBIST,DFT, what is BIST in vlsi?) (0) | 2022.04.05 |

| Back End Flow 란? (what is back end flow in vlsi?) (1) | 2022.04.01 |

| Synthesis 란 무엇일까? (what is synthesis in vlsi?) (2) | 2022.03.30 |