- STA란? -

(Static Timing Analysis)

- timing violation에 대한 모든 path를 확인하여 logic의 timing을 검증하는 방법입니다.

STA를 하는 이유

- Clock이 들어갈 때 즉각적으로 rising이나 falling이 되는 것이 이상적이지만 실제로는 기울어져 들어가게 됩니다.

→ Function 적으로 문제가 없을지라도 timing이 맞지 않으면 불안정한 출력 값이 나오게 됩니다.

Timing path

- STA 진행 시 logic을 timing path로 나누어 검증

- timing path를 구성하는 요소

1) Start point

: timing path의 시작 지점. start point는 input port나 register의 clock pin 이어야 합니다.

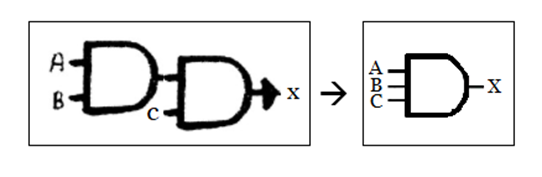

2) Combinational logic

: memory나 register 등이 아닌 buffer, AND, OR로 이루어진 logic입니다.

3) End point

: timing path의 끝 지점. end point는 output port나 register의 input pin 이어야 합니다.

PATH1. input port → register input pin

PATH2. register clock pin → register input pin

PATH3. register clock pin → output port

PATH4. input port → output port

Path의 종류

- Clock path

: 하나 이상의 buffer나 inverter를 거치는 path

- Asynchronous path

: path가 reset에서 시작되거나 다른 종류의 clock을 사용하는 것과 같은 비동기 path

- Multicycle path

: capture가 2 cycle 이상의 주기에서 걸리도록 설계된 path

- False path

: timing constraint를 충족하는 데 필요하지 않는 path

→ 연결된 2개의 mux가 있다고 가정하면 select에 따라 한 개의 mux는 동작하지 않을 수 있습니다.

하지만 tool에서는 동작하지 않는 mux의 path도 고려하기 때문에

이러한 path들을 false path 지정하여 timing을 보지 않도록 해야 합니다.

- Maximum delay : 가장 최악의 조건에서의 delay (최장 경로, delay가 큰 cell 통과 등등..)

- Minimum delay : 가장 최선의 조건에서의 delay (최단 경로, 최적화된 path, delay가 작은 cell 등등..)

Timing violation

- Hold violation : data가 input으로 들어온 후 clock이 너무 빠르게 transition 될 경우 발생하는 violation

- Setup violation : clock이 data 보다 빠르게 들어와 data의 진행 시간을 놓쳤을 때 발생하는 violation

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| OCC란 무엇일까? (what is OCC in vlsi?) (1) | 2022.08.19 |

|---|---|

| LEC란 무엇일까? (what is LEC in vlsi, Formality) (0) | 2022.04.27 |

| Scan(LBIST)란 무엇일까? (what is scan in vlsi, occ, atpg, SA, TD, PLL, At-speed) (0) | 2022.04.15 |

| Leakage power 가 생기는 이유? (logic이 off인데 power가 누설 되는 이유) (0) | 2022.04.13 |

| Low power Techiques란 무엇일까?(what is low power in vlsi, clock gating, isolation, level shift) (0) | 2022.04.12 |