synthesis ?

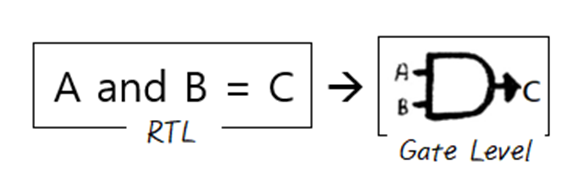

- Synthesis : 합성

- RTL(VHDL, Verilog source)을 gate level의 netlist로 변환하는 단계입니다.

→ 비교적 간단한 RTL 설계를 power, timing과 같은 constraint를 고려하여

gate로 이루어진 netlist로 바꿔주는 중요한 작업입니다.

synthesis를 하는 이유?

1. Gate Level Netlist 얻기 위해

→ Verilog와 같이 글로 설계되어 있는 RTL을 실제 사용하는 gate를 이용하여

gate level netlist로 변환해야 실제 chip 구현(layout)이 가능하기 때문입니다.

2. DFT logic 삽입

→ chip을 test 할 때 외부 test 장치를 사용하면 비용이 많이 들게됩니다.

→ 따라서 비용 절감을 위해 비교적 느린 속도로 logic을 test 해야 합니다.

→ 내부에 test logic을 넣어 비교적 싸고 빠르게 test 할 수 있습니다.

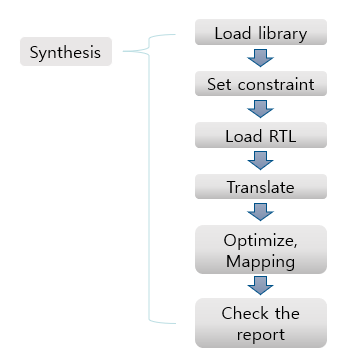

synthesis flow

- synthesis flow는 크게 6가지 단계로 나눌 수 있습니다.

Load lib

- logic을 구성하는 데에 있어 필요한 standard cell, memory, IP 등의 정보가 담겨있는 library를 불러오는 단계입니다.

→ 예를 들어 AND gate를 사용해야 할 때 사용할 AND gate의 size, in/output의 개수 등의 정보가 필요합니다.

→ 하지만 RTL 에서는 logic의 connect 정보와 같이 비교적 간단한 정보만이 기술되어 있기 때문에

해당 정보가 기술되어 있는 library를 불러오는 단계가 필요합니다.

Set constraint

- clock, timing, power의 정보와 같은 block의 constraint를 setting 해주는 단계입니다.

→ 글로 작성되어 있는 RTL code를 layout을 위해 gate 단위로 바꾸는 것이기 때문에

register, net 등의 delay나 power에 대해 setting이 필요합니다.

→ 예를 들어 어떤 memory가 사용될 때 이 memory가 '어떤 clock을 사용하는지' '어느 정도의 power가 필요한지' 등을

setting 해주는 단계입니다.

Load RTL

- RTL(verilog, hdl) code를 불러오는 단계입니다.

Translate

- Gate level로 변환하는 단계입니다.

→ RTL code를 읽어온 후 바로 합성을 진행하는 것이 아닌

gate의 정보나 종류 등을 고려하지 않고 gate level로 변환합니다.

→ ‘어떻게 연결되어 있는지’ ‘어떤 port가 연결되어 있는지’ 등을 광범위하게 확인하기 위함입니다.

→ 실수를 줄이고 정확하고 정교한 합성을 하기 위한 단계입니다.

Optimize

- Logic을 최대한 간단하게 만드는 단계입니다.

→ synthesis를 진행하다 보면 function 적으로 필요 없거나 간단하게 나타낼 수 있는 부분이 존재합니다.

→ 원래도 복잡한 반도체 logic을 필요 이상으로 복잡하게 구성할 필요가 없기 때문에 Optimize 단계를 꼭 거쳐야합니다.

Mapping

- 제조 공정 제약에 맞게 logic(gate, memory 등)을 place 하는 단계입니다.

→ 삼성, TSMC와 같이 반도체 제조 업체의 공정에 맞게 구성하여야 합니다.

→ 예를 들어 OR gate를 사용할 때 어떤 공정은 정사각형 모양을 사용할 수도 있고

어떤 공정은 동그라미 모양을 사용할 수도 있습니다.

따라서 공정 제약에 맞는 library와 place가 필요합니다.

Check the report

- 합성이 잘 진행되었는지 확인하는 단계이다.

→ congestion과 timing 확인

→ memory, cell, IP 등이 각각 block 내에서 차지하는 area는 어느 정도인지

→ power 소모량은 얼마나 되는지 등을 확인할 수 있습니다.

synthesis의 종류

- 최근에는 공정이 복잡해짐에 따라 layout까지 고려하여 (gate들의 배치, net delay 등등..)

synthesis를 진행하는 경우도 있습니다.

→ synthesis 방법에 따라 physical library도 필요한 경우가 있습니다.

- DC : pysical적인 wire만 고려하여 synthesis 진행

- ZWLM : wire의 delay가 0이라고 가정하고 synthesis 진행

- DCT : 가상의 배치를 통해 synthesis 진행

- DCG : 실제적인 배치를 고려하여 synthesis 진행

synthesis를 할 때 사용되는 대표적인 tool

- Synopsys의 Design compiler

- Cadence의 RTL Compiler

- Simens의 EDA

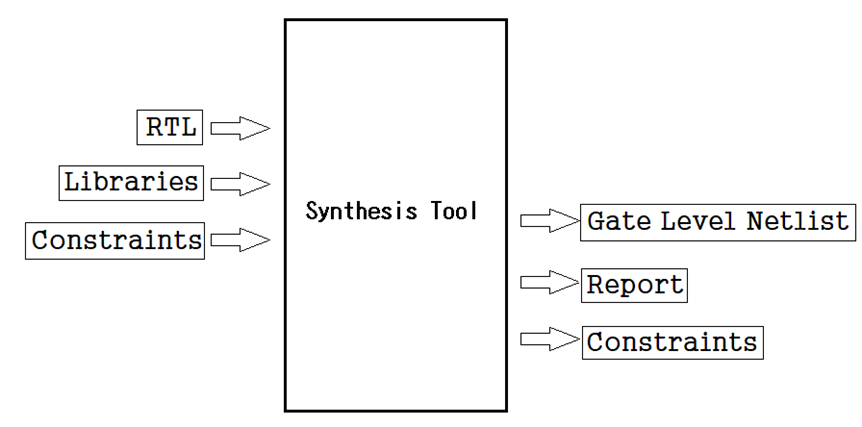

synthesis flow 정리

synthesis input (synthesis 진행 시 필요한 정보(파일))

- RTL code

- Libraries

- Constraints (UPF (power 정보), SDC (clock 정보))

- etc ..

synthesis output

(synthesis 완료 시 얻는 정보)

- Gate Level Netlist

- Timing report, Area report

- UPF

- SDC

- etc ..

synthesis report

- congestion report

- timing report

- power report

- area report

- etc ..

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| Leakage power 가 생기는 이유? (logic이 off인데 power가 누설 되는 이유) (0) | 2022.04.13 |

|---|---|

| Low power Techiques란 무엇일까?(what is low power in vlsi, clock gating, isolation, level shift) (0) | 2022.04.12 |

| BIST, BIRA, BISR란? (MBIST,DFT, what is BIST in vlsi?) (0) | 2022.04.05 |

| Back End Flow 란? (what is back end flow in vlsi?) (1) | 2022.04.01 |

| Front-End Flow 란? (VLSI, FE flow, what is front end flow in vlsi?) (0) | 2022.03.28 |