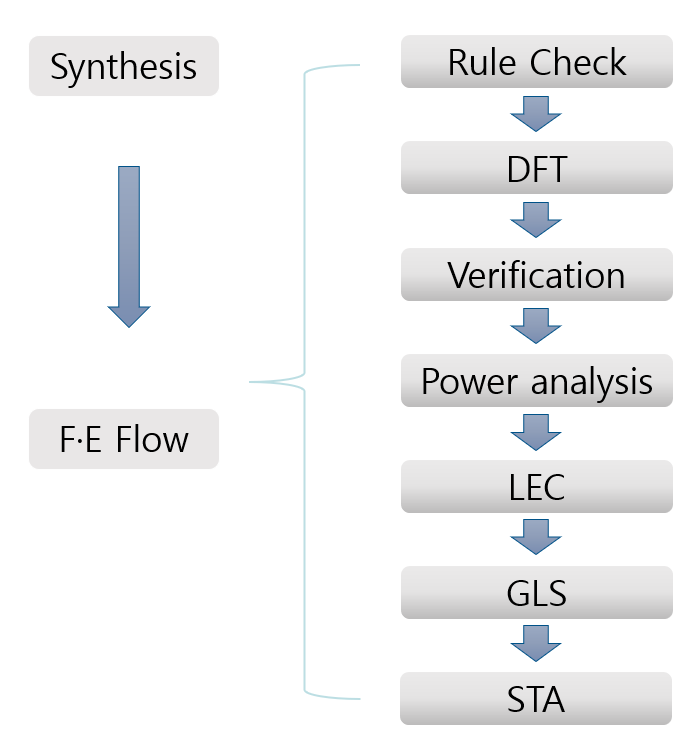

- Front-End Flow -

- ASIC design flow는 DFT를 담당하는 Front End와 Layout을 하는 Back End가 있습니다.

그중 Front End Flow에서는 test logic을 삽입하고 회로 검증을 진행합니다.

synthesis

- Gate-Level (buffer, latch, and gate 등)로 바꿔주는 단계입니다.

- 처음 팹리스 업체에서의 chip 설계는 verilog와 같은 RTL(Register-Transfer Level) code로 이루어져 있지만

chip을 만들기 위해서는 Layout이 가능한 Gate-Level netlist로 바꿔줘야 합니다.

(글로 설계되어 있는 logic을 실제 회로의 모양으로 바꿔주는 단계입니다.)

- Synthesis 중 중요한 점은 최대한 회로를 간단하게 표현하는 optimization과

파운드리 공정에 맞는 library로 mapping 시킨다는 점입니다.

* gate-level netlist : gate로 표현 된 netlist

* library : 해당 공정에서 정해 놓은 소자들의 모양이 있는데, 그것들을 모아 놓은 것.

(예를 들어, and gate는 네모 모양의 3개의 input이 있는 and gate는 A and gate를 써라 등등..)

* mapping : 회로에 있는 소자와 library에 있는 모양을 연결시켜주는 것

Rule check

- Synthesis 이후, 설계된 회로에 기능적인 결함이 없는지 확인하는 단계입니다.

- Logic의 rule을 check하는 LDRC, power issue를 check하는 LPRC가 있습니다.

- LDRC : floating net, tie 등 회로가 동작하는 데에 있어 문제가 발생할 수 있는 부분이 있는지 확인하는 단계입니다.

- LPRC : power가 정해진 조건에 맞게 공급되고 있는지 확인하는 단계입니다.

DFT

- Chip을 만든 후 chip 전체를 외부 장치를 이용하여 test 하려면 많은 비용과 시간이 필요합니다.

→ 따라서 logic 내부에 logic을 test 할 수 있는 DFT logic를 넣게 되면 비교적 적은 비용과 시간으로 test 할 수 있습니다.

- DFT에는 Memory를 test 할 수 있는 MBIST, logic을 test 할 수 있는 SCAN(LMIBST)이 있습니다.

Verification

- Synthesis 이후 또는 DFT logic 삽입 후 회로가 function 적으로 문제가 없는지 test 하는 단계입니다.

Power analysis

- Logic을 test 하는 것에 있어서 가장 중요한 것은 최상의 조건이 아닌 최악의 조건으로 test 하는 것입니다.

- chip이 만들어진 후 어떤 조건에서도 목적에 맞게 동작이 되어야 하기 때문에

최악의 조건에서도 동작할 수 있도록 test 하는 것입니다.

- Power analysis는 여러 가지 조건에서의 power 소모량을 분석하는 단계입니다.

LEC

- Synthesis 이후 RTL netlist와 gate level netlist가 function 적으로 달라진 것이 있는지 확인하는 단계입니다.

- 또한 DFT 단계를 거치면서 test logic이 추가됐기 때문에 logic이 달라지게 됩니다.

→ 하지만 test logic은 function 적인 부분에서 영향을 끼치면 안됩니다.

따라서 test logic을 넣기 전과 후를 비교하여 function 적으로 달라진 것이 있는지 test 해야 합니다.

GLS

- Memory와 logic을 simulation을 하는 단계입니다.

→ Input에 test pattern을 넣어 output을 추출합니다.

→ Test pattern을 이용한 output의 결괏값과 실제 동작 결괏값(golden output)이 같은 지 비교합니다.

STA

- Clock이 register나 net 등을 거치게 되면 delay가 발생합니다.

- 이러한 delay 때문에 violation이 발생하는지 확인하는 단계입니다.

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| Leakage power 가 생기는 이유? (logic이 off인데 power가 누설 되는 이유) (0) | 2022.04.13 |

|---|---|

| Low power Techiques란 무엇일까?(what is low power in vlsi, clock gating, isolation, level shift) (0) | 2022.04.12 |

| BIST, BIRA, BISR란? (MBIST,DFT, what is BIST in vlsi?) (0) | 2022.04.05 |

| Back End Flow 란? (what is back end flow in vlsi?) (1) | 2022.04.01 |

| Synthesis 란 무엇일까? (what is synthesis in vlsi?) (2) | 2022.03.30 |