- OCC란? -

(On-chip Clock Controllers)

- 외부 장치(ATE)에서 오는 clock을 제어하기 위한 clock controller

- 2개의 clock이 필요한 at-speed test 진행 시 사용됩니다.

At-speed test

- Logic을 기능적으로 test 할 때(SCAN, LBIST) 원래 동작하는 clock보다 느린 clock을 사용하여 test 하게 됩니다.

→ 하지만 transition delay fault를 test 할 때는 실제 logic이 동작하는 속도의 clock으로 test를 진행해야 합니다.

→ 실제 logic의 동작 속도로 test 하는 것을 at-speed test라고 합니다.

느린 clock으로 test를 진행하는 이유

- dynamic power의 손실을 줄이기 위해

transition delay test에서 at-speed test가 필요한 이유

- stuck at fault를 test 할 때는 delay와 상관없이 값의 고착만 확인하면 되기 때문에 clock의 속도는 의미가 없습니다.

하지만 transition delay fault는 delay를 test 하기 때문에 실제 logic의 동작 속도로 test를 진행해야 합니다.

PLL clock (Phase-Locked Loop)

- Clock의 위상이 흔들리지 않게 고정시켜 줍니다.

→ clock의 위상이 흔들리지 않게 함으로서 clock을 안정화 시켜주고 품질을 높여줍니다.

→ 입력으로 받은 clock의 주파수를 chip에서 사용할 주파수로 바꿔 줄 수 있습니다.

Scan chain

- Logic을 test 할 때 test data를 shift 하기 위하여 사용되는 설계 구조

- 여러 개의 Scan flip-flop이 연속적으로 연결되어 형성됩니다.

- 처음 flip-flop의 input은 data를 받고 마지막 flip-flop의 output은 data를 추출하는 데 사용됩니다.

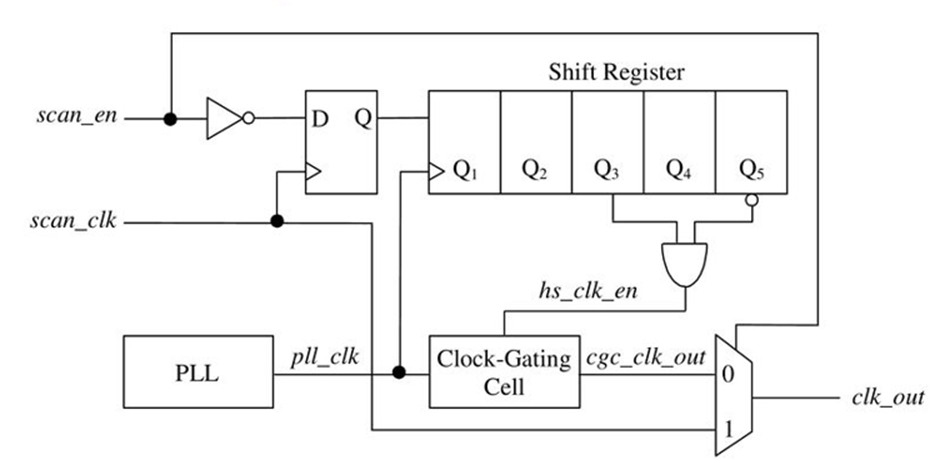

OCC구조

- SE에 1을 주면 register에 0 shift

- SE에 0을 주면 register에 1 shift

| Q3 | Q2 | Q1 | ||

| SE = 1 | 0 | 0 | 0 | |

| SE = 0 | 1 | 0 | 0 | = PLL clock |

| 1 | 1 | 0 | = PLL clock | |

| 1 | 1 | 1 | ||

| SE = 1 | 0 | 1 | 1 |

1. SE에 1을 주고 flip flop을 모두 0으로 채웁니다.

2. flip flop에 0이 모두 채워졌을 때 SE에 0을 주게 되면 PLL clock이 딱 2번만 들어가게 되는 구조입니다. (capture)

'▶ Technology > ▷ VLSI' 카테고리의 다른 글

| STA란 무엇일까? (What is STA in vlsi?) (0) | 2022.10.14 |

|---|---|

| LEC란 무엇일까? (what is LEC in vlsi, Formality) (0) | 2022.04.27 |

| Scan(LBIST)란 무엇일까? (what is scan in vlsi, occ, atpg, SA, TD, PLL, At-speed) (0) | 2022.04.15 |

| Leakage power 가 생기는 이유? (logic이 off인데 power가 누설 되는 이유) (0) | 2022.04.13 |

| Low power Techiques란 무엇일까?(what is low power in vlsi, clock gating, isolation, level shift) (0) | 2022.04.12 |